JY Electronics announced today the launch of an ultra-low capacitance ESD protection device for high-speed signal lines and high-frequency antennas—the TT0501SZ. This product utilizes the latest ultra-low capacitance platform and advanced packaging technology to protect ultra-high-speed lines and high-frequency antennas, making it highly suitable for applications in USB Type-C, Thunderbolt, HDMI, and high-frequency antennas.

Applications include desktop computers, laptops, gaming consoles, high-definition TVs, monitors, wearable devices, TWS (True Wireless Stereo), and wireless communication. The product is now available for bulk shipment.

Highlights of the TT0501SZ Product:

1、Features a CSP0402-2L package (0.4 mm × 0.2 mm), which is compact in size, saving a significant amount of PCB area and reducing costs;

2、With an ultra-low capacitance of 0.18 pF, it ensures the integrity of high-speed signals and suppresses high harmonic distortion of wireless signals.

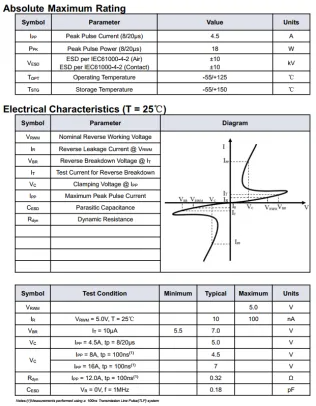

3、Employs our company’s unique deep snapback leading-edge patent technology, with a clamping voltage of 5V@IPP=4.5A under 8/20μs waveform testing. Compared to non-snapback and shallow snapback devices, deep snapback devices provide better protection performance for circuits.

4、Meets the ESD endurance shock requirements of 10kV contact discharge and 10kV air discharge as tested by IEC 61000-4-2.

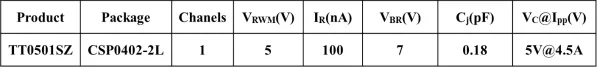

Key Parameters of TT0501SZ:

Parameter Overview

Layout Design Considerations:

1、Place ESD protection devices as close as possible to I/O connectors to reduce ESD grounding paths and enhance protection performance.

2、PCB routing should preferably have rounded corners or 45-degree angles, avoiding right-angle wiring to prevent unnecessary reflections.

3、Maintain equal trace lengths between the positive and negative lines of differential data channels to avoid the generation of common mode noise and impedance mismatch.